指令级并行(Instruction-Level Parallelism, ILP)是现代计算机体系结构设计的核心概念之一,它旨在通过硬件技术提高程序的执行效率,使多条指令能够在同一时间段内并行执行,从而提升处理器的性能。本章将聚焦于硬件方法,探讨计算机体系结构如何通过硬件层面的设计来开发和利用指令级并行。

1. 指令级并行的定义与重要性

指令级并行是指在一个程序中,多条指令之间不存在数据依赖或控制依赖,因而可以同时执行。硬件方法通过设计复杂的处理器微架构来识别和利用这种并行性,例如流水线技术、超标量架构和动态调度等。ILP的开发对于打破传统顺序执行瓶颈至关重要,尤其是在高性能计算和嵌入式系统中,它能够显著加速指令吞吐率,提升整体计算能力。

2. 硬件方法的核心技术

硬件方法开发ILP主要包括以下几个方面:

- 流水线技术:将指令执行过程划分为多个阶段(如取指、译码、执行、访存、写回),使不同指令在不同阶段重叠执行,从而提高吞吐率。但流水线可能面临结构冒险、数据冒险和控制冒险等问题,需要硬件机制(如旁路、分支预测)来解决。

- 超标量架构:处理器在每个时钟周期内可以发射并执行多条指令,通过硬件动态调度指令顺序,以最大化并行性。超标量处理器通常包含多个功能单元(如ALU、FPU),能够同时处理不同类型的指令。

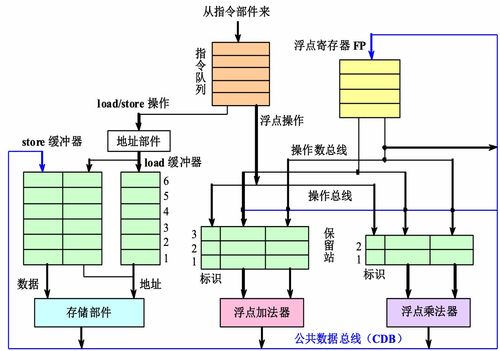

- 动态调度与乱序执行:硬件通过重排序缓冲区(ROB)和保留站(Reservation Station)等机制,动态检测指令依赖关系,将无依赖的指令提前执行,以隐藏延迟并提高资源利用率。

- 分支预测技术:为了减少控制冒险带来的流水线停顿,硬件采用分支预测器(如静态预测、动态预测)来预测分支指令的走向,确保指令流的连续性。

- 寄存器重命名:通过硬件映射逻辑寄存器到物理寄存器,消除写后写(WAW)和写后读(WAR)假依赖,增加指令并行执行的机会。

3. 硬件方法的优势与挑战

硬件方法开发ILP具有显著优势:它无需修改软件代码,通过透明化的硬件优化即可提升性能;能够适应动态的程序行为,实时调整指令调度。硬件方法也面临挑战:复杂的硬件设计会增加芯片面积、功耗和成本;并行性的挖掘受限于指令间的固有依赖,可能遭遇收益递减;硬件错误(如分支预测失败)可能导致性能下降。

4. 实际应用与未来发展

在实际计算机系统中,硬件方法已广泛应用于现代处理器,如Intel的Core系列和ARM的Cortex系列。这些处理器结合了多种ILP技术,以实现高性能和能效平衡。随着人工智能和物联网的发展,硬件方法将继续演进,例如通过更智能的预测算法、异构计算架构以及近似计算技术,来应对日益复杂的计算需求。

硬件方法是开发指令级并行的关键途径,它通过创新的微架构设计,推动了计算机性能的持续提升。理解这些技术不仅有助于优化处理器设计,也为软件开发提供了底层性能洞察,是计算机体系结构学习中不可或缺的一环。